OpenMV Cam RT1062

AED575.00

- ARM® 32-bit Cortex®-M7 CPU w/ Double Precision FPU

- 32KB Stack

- Operating Temperature: 0°C to 70°C

- Format: 1/3″

- Aperture: F2.0

The OpenMV Cam RT1062 is a small, low power, microcontroller board which allows you to easily implement applications using machine vision in the real-world. You program the OpenMV Cam in high level Python scripts (courtesy of the MicroPython Operating System) instead of C/C++. This makes it easier to deal with the complex outputs of machine vision algorithms and working with high level data structures. But, you still have total control over your OpenMV Cam and its I/O pins in Python. You can easily trigger taking pictures and video on external events or execute machine vision algorithms to figure out how to control your I/O pins.

The RT1062 ARM Cortex M7 processor runs at 600 MHz with 32MBs SDRAM + 1MB of SRAM and 16 MB of program/storage flash. One of the big differences between the H7 Plus is the inclusion of WIFI on the RT1062.

About this item

- High-Speed Processor: Features a 600 MHz ARM Cortex-M7 with 32MB SDRAM and 16MB flash for fast, reliable machine vision applications, running up to 40 FPS at QVGA resolutions.

- Versatile Connectivity: Includes USB-C, WiFi (802.11 a/b/g/n), Bluetooth v5.1, and Ethernet with PoE, offering seamless communication for diverse projects.

- Customizable Camera Module: Comes with a 5MP OV5640 sensor and M12 lens mount, supporting 2592×1944 resolution and optional modules for global shutter or thermal imaging.

- Advanced I/O and Low Power: 14 I/O pins with SPI, I2C, UART, ADC, and deep sleep mode consuming only 30µA for efficient, power-sensitive operations.

- Feature-Packed Design: Includes a secure cryptographic element, accelerometer, LiPo battery charging, RGB LEDs, and professional module support for advanced use cases.

Related products

DFRobot Gravity Lab Grade Analog Dissolved Oxygen Sensor / Meter Kit For Arduino

In stock

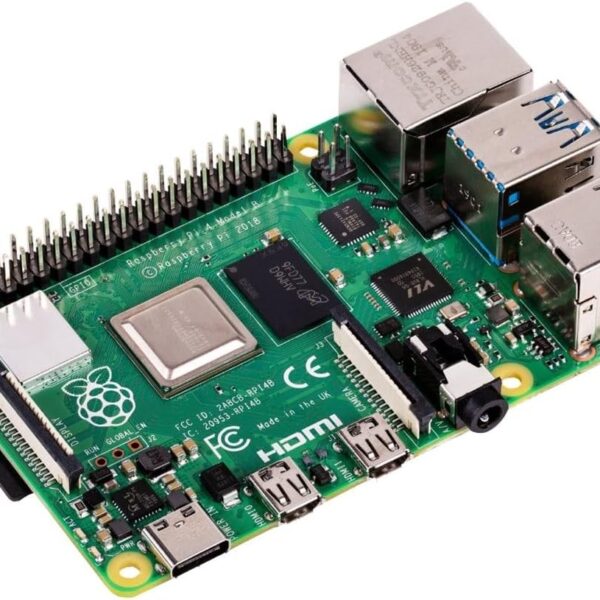

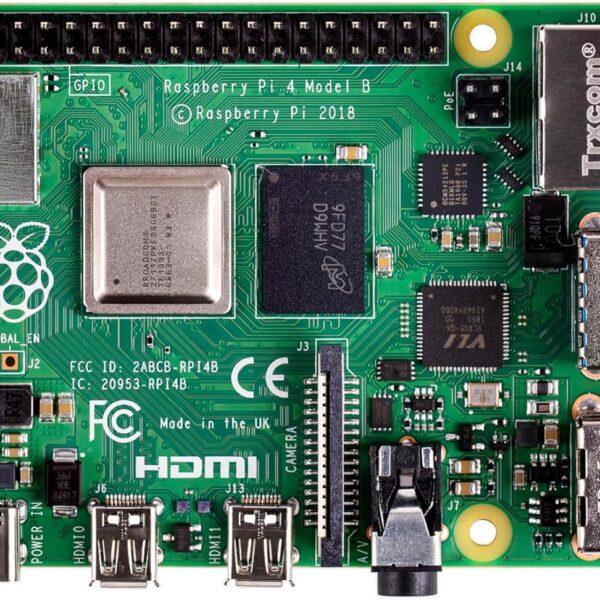

Waveshare 7inch 1024×600 Capacitive Touch Display for Raspberry Pi, DSI Interface

In stock

Zigbee XBee Module S2C 802.15.4 2mW with Wire Antenna XB24CZ7WIT-004

In stock

Reviews

Clear filtersThere are no reviews yet.